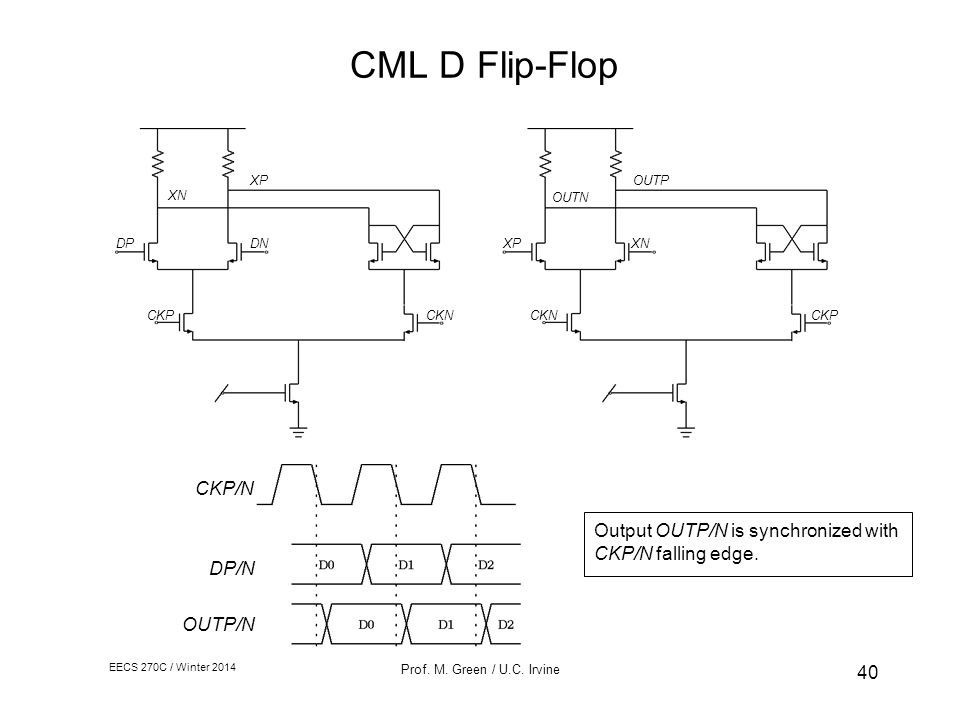

Help me calculate the device size of CML/SCL latch design and simulate the gain of it | Forum for Electronics

Amazon.com | ANBOVER Womens High Wedge Beach Sandals Summer Thong Flip Flops Platform, Black, 8 | Flip-Flops

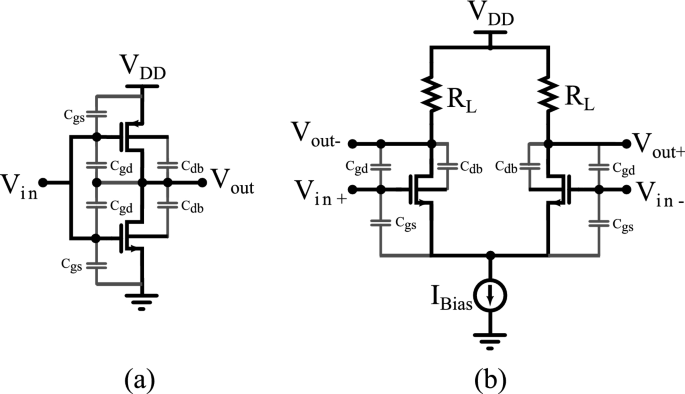

An improved current mode logic latch for high‐speed applications - Kumawat - 2020 - International Journal of Communication Systems - Wiley Online Library

An improved current mode logic latch for high‐speed applications - Kumawat - 2020 - International Journal of Communication Systems - Wiley Online Library

Amazon.com: YALFJV Womens Shoes Black Wedges Sandals flip Flops for Women Walking Royal Blue Sandals Nude Sandals for Women Flat White Platform Heels Chunky Women Slides Ladies Strap Sandals Sandals for Women :